# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2018/0269191 A1 ENGLAND et al.

Sep. 20, 2018 (43) Pub. Date:

## (54) MICRO-LED DISPLAY ASSEMBLY

(71) Applicant: GLOBALFOUNDRIES INC., Grand Cayman (KY)

(72) Inventors: Luke ENGLAND, Saratoga Springs, NY (US); Bartlomiej Jan PAWLAK, Leuven (BE)

(21) Appl. No.: 15/459,336

(22)Filed: Mar. 15, 2017

#### **Publication Classification**

(51) Int. Cl. H01L 25/16 (2006.01)H01L 25/075 (2006.01)

| H01L 25/00 | (2006.01) |

|------------|-----------|

| H01L 33/62 | (2006.01) |

| H01L 33/32 | (2006.01) |

(52) U.S. Cl.

CPC ...... H01L 25/167 (2013.01); H01L 25/0753 (2013.01); H01L 27/1214 (2013.01); H01L 33/62 (2013.01); H01L 33/32 (2013.01); H01L 25/50 (2013.01)

#### (57)**ABSTRACT**

The present disclosure relates to semiconductor structures and, more particularly, to a micro-light emitting diode (LED) display assembly and methods of manufacture. The structure includes an interposer and a plurality of micro-LED arrays each of which include a plurality of through-vias connecting pixels of the plurality of micro-LED arrays to the interposer.

FIG. 4

FIG. 5

FIG. 6

#### MICRO-LED DISPLAY ASSEMBLY

#### FIELD OF THE INVENTION

[0001] The present disclosure relates to semiconductor structures and, more particularly, to a micro-LED display assembly and methods of manufacture.

### BACKGROUND

[0002] Inorganic light emitting diodes (ILED) are light emitting diodes made from semiconductor material. It is possible to produce a variety of different colors using an ILED, including red, green, yellow and blue. In operation, the ILED emits light when a forward bias voltage is applied to a P-N junction of the semiconductor material.

[0003] LED devices for display systems require high pixel placement density on a large surface. However, conventional manufacturing methods for LEDs have a challenge to meet yield requirements, especially for larger display sizes. Also, higher costs are associated with next generation displays due to poor wafer area utilization. As to this latter point, the use of a single die for large LED displays and image sensor arrays leaves significant unused space around edges of the wafer in partial field areas.

### **SUMMARY**

[0004] In an aspect of the disclosure, a structure comprises: an interposer; and a plurality of micro-LED arrays each of which comprise a plurality of through-vias connecting pixels of the plurality of micro-LED arrays to the interposer.

[0005] In an aspect of the disclosure, a structure, comprises: an interposer comprising a plurality of through vias; a plurality of micro-LED arrays each of which comprise a plurality through-vias connecting to each pixel of the plurality of micro-LED arrays; and a back-end of the line interposer comprising a wiring scheme which connects the through-vias of each of the pixels to the through vias of the interposer.

[0006] In an aspect of the disclosure, a method comprises: forming a plurality of through vias in a substrate connecting to pixels of micro-LED arrays; and connecting the pixels of each of a plurality of micro-LED arrays to a single interposer with the through vias aligned with connections of the interposer.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0007] The present disclosure is described in the detailed description which follows, in reference to the noted plurality of drawings by way of non-limiting examples of exemplary embodiments of the present disclosure.

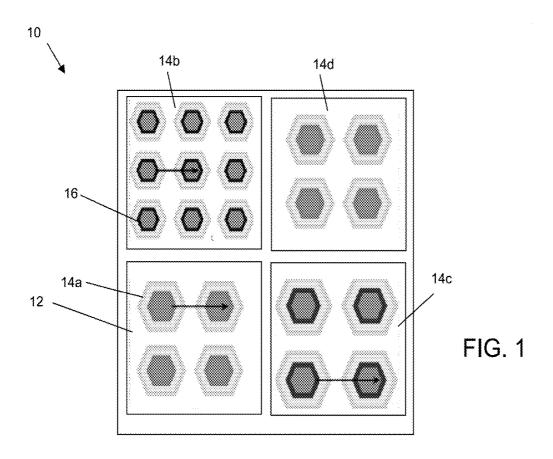

[0008] FIG. 1 shows a pixel design in accordance with aspects of the present disclosure.

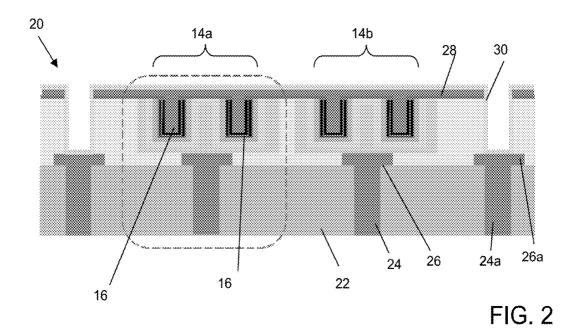

[0009] FIG. 2 shows a cross-sectional view of a micro-LED assembly and respective fabrication processes in accordance with an aspect of the present disclosure.

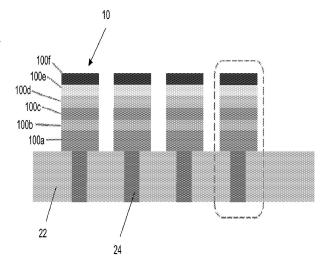

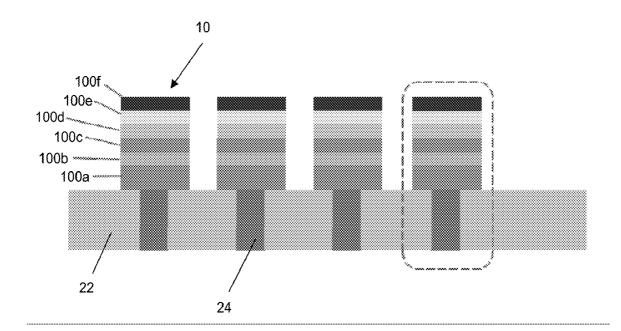

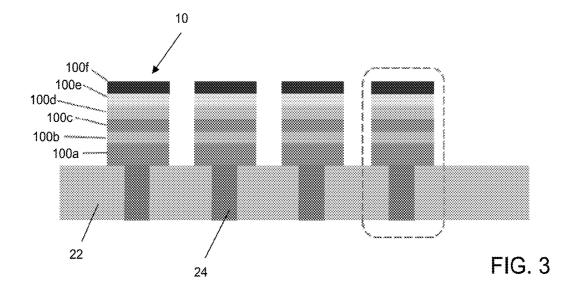

[0010] FIG. 3 shows an alternative structure and respective fabrication processes in accordance with aspects of the present disclosure.

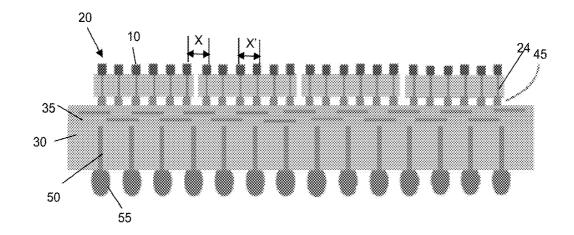

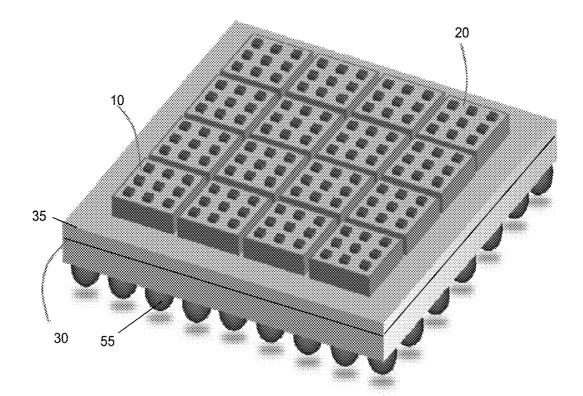

[0011] FIG. 4 shows a cross-sectional view of the micro-LED display assembly in accordance with aspects of the present disclosure. [0012] FIG. 5 shows a perspective view of the micro-LED display assembly in accordance with aspects of the present disclosure.

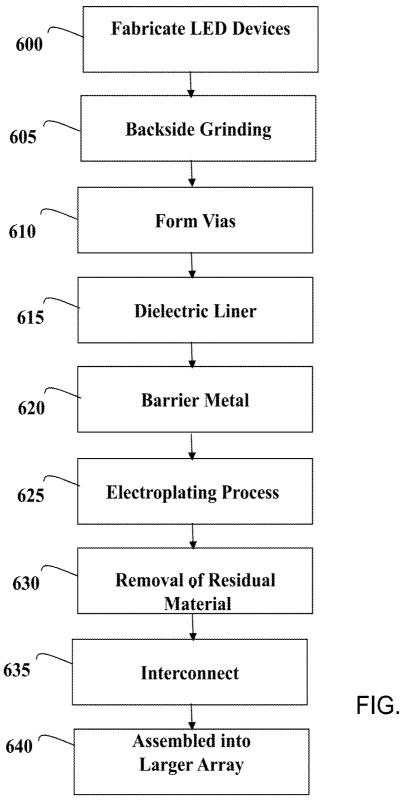

[0013] FIG. 6 shows a flowchart of the fabrication processes in accordance with aspects of the disclosure

#### DETAILED DESCRIPTION

[0014] The present disclosure relates to semiconductor structures and, more particularly, to a micro-LED display assembly and methods of manufacture. More specifically, the present disclosure relates to a micro-LED display assembly composed of multiple small micro-LED arrays placed in a larger array using through silicon via technologies. That is, the micro-LED display assembly uses multiple small dies in an array to replace one large array. The micro-LED display assembly can be used with, e.g., 2.5D and 3D technologies. [0015] In embodiments, each small micro-LED array comprises through silicon via (TSV) technologies for mounting onto a substrate to form a larger display assembly. In embodiments, the TSVs are connected to each individual micro-LED, e.g., pixel. The TSV micro-LED array devices can be connected using a silicon or glass interposer, or directly to a pixel driver. In embodiments, the silicon interposer allows for direct integration of pixel driver circuits; whereas, the glass interposer would require a separate pixel driver. In embodiments, the multiple small micro-LED arrays provides high dense wiring to each TSV/micro-LED connection.

[0016] Advantageously, the micro-LED display assembly provides improved (e.g., high) yields for large display sizes, compared to using a single, larger pixel array. This is due to the fact that several small dies can be assembled to collectively form the larger LED array; instead of a single large die. More specifically, if a failure is found on a single large die, the entire die will need to be discarded; whereas, as presently disclosed herein, if a single failure is found on a smaller die, only that single, smaller die will need to be discarded. This will significantly reduce costs and improve yields, as it is less expensive to discard smaller dies than a larger die upon a failure of a pixel.

[0017] In addition, manufacturing costs can be significantly reduced by more efficiently using the space on the wafer. For example, by using smaller dies, it is now possible to more efficiently utilize the unused space around edges of the wafer. Moreover, the micro-LED display assembly described herein provides improved reliability by using an interposer which acts as a stress buffer between the board and the micro-LED dies.

[0018] The micro-LED display assembly of the present disclosure can be manufactured in a number of ways using a number of different tools. In general, though, the methodologies and tools are used to form structures with dimensions in the micrometer and nanometer scale. The methodologies, i.e., technologies, employed to manufacture the micro-LED display assembly of the present disclosure have been adopted from integrated circuit (IC) technology. For example, the micro-LED display assembly is built on wafers and are realized in films of material patterned by photolithographic processes on the top of a wafer. In particular, the fabrication of the wafer bond pad structures uses three basic building blocks: (i) deposition of thin films of material on a substrate, (ii) applying a patterned mask on top of the films by photolithographic imaging, and (iii) etching the films selectively to the mask.

[0019] FIG. 1 shows a single pixel used in a micro-LED assembly in accordance with aspects of the present disclosure. It should be understood by those of skill in the art that FIG. 1 (and other figures described herein) can also represent a layout pattern for any repeatable design structure such as memory cell arrays, etc. In FIG. 1, a pixel 10 comprises a contact plate or electrode 12 with four sub-pixels 14a-14d. In embodiments, the contact plate or electrode 12 can be a nano-wire contact and reflector plate composed of opaque material such as metal, for example, to maximize light emitting from the sub-pixels 14a-14d.

[0020] In embodiments, the pixel 10 has a dimension of  $6.35 \,\mu\text{m} \times 6.35 \,\mu\text{m}$  and the sub-pixels 14a-14d have a dimension of  $3.175 \,\mu\text{m} \times 3.175 \,\mu\text{m}$ ; although other dimensions are also contemplated herein. As should be understood by those of skill in the art, multiple of these pixels 10 can be formed on a single micro-LED assembly in accordance with aspects of the present disclosure. For example, a micro-LED assembly implemented herein can include 1000 pixels by 1000 pixels; although other pixel counts are contemplated herein depending on the assembly technology or tools.

[0021] Still referring to FIG. 1, the sub-pixels 14a-14d comprise, in one illustrative example, a RGB pixel design used in an inorganic light emitting diode (ILED). In embodiments, each of the sub-pixels 14a-14d can have a different number of nano-wires 16 composed of different materials to emit a certain color, e.g., wavelength. By way of non-limiting example, (i) for green light, there can be four nano-wires 16 for sub-pixels 14a, 14d, (ii) for blue light, there can be nine nano-wires 16 for sub-pixel 14b, and (iii) for red light, there can be four nano-wires 16 for sub-pixel 14c. Although sub-pixel 14d is shown to be redundant to sub-pixel 14a, it should be understood that sub-pixel 14d can be redundant to any of the sub-pixels 14a-14c. Alternatively, sub-pixel 14d can be left empty, e.g., devoid of any nano-wires.

[0022] Although not critical to the understanding of the present disclosure, the nano-wires 16 can be composed of different materials in order to provide different wavelengths. For example, Table 1 below shows exemplary combinations of semiconductor materials that can be utilized for the nano-wires.

TABLE 1

| Color | Wavelength            | Semiconductor Material                                                                                                                                                 |

|-------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RED   | 610 < λ < 760         | Aluminum gallium arsenide (AlGaAs)<br>Gallium arsenide phosphide (GaAsP)<br>Aluminum gallium indium phosphide<br>(AlGaInP)<br>Gallium(III) phosphide (GaP)             |

| GREEN | 500 < λ < 570         | Gallium(III) phosphide (GaP) Aluminum gallium indium phosphide (AlGaInP) Aluminum gallium phosphide (AlGaP) Indium gallium nitride (InGaN)/ Gallium(III) nitride (GaN) |

| BLUE  | $450 < \lambda < 500$ |                                                                                                                                                                        |

[0023] FIG. 2 shows a cross-sectional view of a micro-LED assembly and respective fabrication processes in accordance with an aspect of the present disclosure. As shown in FIG. 2, the micro-LED assembly 20 includes sub-pixels 14a, 14b, each having a plurality of nanowires 16. In the example

shown, the cross-sectional view of the micro-LED assembly 20 shows sub-pixels 14a, 14b for each pixel 10a, 10b.

[0024] As further shown in FIG. 2, the micro-LED assembly 20 further includes a substrate 22 with a plurality of TSVs 24 connected to a metal pad 26, e.g., copper pad, in electrical connection with each of the pixels 10a, 10b (e.g., sub-pixels 14a, 14b). As shown, a single TSV 24 is used per pixel, with a diameter of the TSV 24 about ½ a pixel pitch. For example, in an illustrative embodiment, the TSV 24 can have a diameter/width of about less than 3 µm for a pixel that has a pitch of about 6 µm; although smaller dimensions are possible with thinner dies. In embodiments, the pad 26 can be in direct electrical communication with pGaN sub-pixels 14a, 14b, with all pixels sharing a blanket nGaN connection 28, or vice versa. In this representation, the pads 26a and TSVs 24a can be connected to a conductive terminal layer 30. In this way, it is not necessary to have a separate TSV or conductive terminal for each pixel.

[0025] FIG. 3 shows an alternative structure and respective fabrication processes in accordance with aspects of the present disclosure. In this structure, the pixels 10 are schematically represented as stacked structures composed of a plurality of layers 100a-100f, each of which are connected to a TSV 24 formed in the substrate 22. In embodiments, the layers include: nGaN 100a, lnGaN 100b, pGaN 100c, a terminal layer 100d, a phosphorous layer 100e and a color filter 100f. It should be recognized that these layers are provided as illustrative examples and should not be considered limiting features of the present disclosure. For simplicity of illustration, the common pGaN terminal wired to separate TSVs is not shown.

[0026] In each of the representations of FIG. 2 and FIG. 3, the ILED wafer is formed separately, then bonded to the TSV carrier wafer (e.g., wafer 22). Also, the TSVs 24 can be formed by a conventional backside grinding process followed by a deep Si etch, e.g., Bosch etch, to form vias, aligned with and exposing the pads formed on the front side of the wafer (and which are in electrical contact with the pixels). The vias are then coated with dielectric liner, e.g., an inorganic material such as  $\mathrm{SiO}_2$ . In embodiments, the dielectric liner would be deposited to a thickness of about 200 nm; although other thicknesses are contemplated herein. A barrier metal, e.g., Ta or TiN, can be formed over the dielectric liner to prevent Cu diffusion into the oxide and wafer. A seed layer can be sputtered onto the barrier metal, followed by an electroplating process, e.g., Cu electroplating process. Any residual material can be removed by a chemical mechanical polishing step. It should be understood that reference numeral 24 represents the different materials within the via,

[0027] FIG. 4 shows a cross-sectional view of the micro-LED display assembly in accordance with aspects of the present disclosure. More specifically, FIG. 4 shows a plurality of micro-LED assemblies 20 mounted on an interposer 30. In embodiments, the interposer 30 can be an Si interposer composed of integrated ILED pixel driver circuits. In alternative embodiments, the interposer 30 can be a glass interposer or an active die. In embodiments, the plurality of micro-LED assemblies 20, e.g., at least two ILED dies containing the TSV interconnects, are placed with equal spacing on the interposer 30 as further described herein.

[0028] A back end of the line (BEOL) wiring 35 is positioned (e.g., bonded) between the plurality of micro-LED assemblies 20 and the interposer 30. In embodiments,

the BEOL wiring **35** includes a wiring scheme which electrically connects each of the pixels **10** of the plurality of micro-LED assemblies **20** to the interposer **30**. More specifically, each of the TSVs **24** of each pixel of each micro-LED assembly **20** connects to a micropillar interconnect **45** which, in turn, connects to the wiring scheme of the BEOL wiring **35**. In embodiments, the pitch of the micropillar interconnect **45** will match the TSVs **24**, e.g., 5-10 µm pitch. As should be understood by those of skill in the art, the micropillar interconnect **45** can be a conventional controlled collapse chip connection (C4) solder interconnect. In alternate embodiments, the plurality of micro-LED assemblies **20** can be gang bonded to the BEOL wiring **35**.

[0029] Still referring to FIG. 4, the wiring scheme of the BEOL wiring 35 is connected to a plurality of TSVs 50 of the interposer 30. The TSVs 50 of the interposer 30 can be manufactured in the same manner as the TSVs 24 for each pixel of the micro-LED assemblies 20. In connecting the plurality of TSVs 50 of the interposer 30, in embodiments, the across die pixel pitch/spacing "X" is preferably equal to the within die pixel pitch/spacing "X" so as not to disrupt viewing of the overall pixel array. In further embodiments, the interposer 30 includes solder connections 55 in electrical contact with the TSVs 50 of the interposer 30. In this way, the solder connections 55 provide external interconnects for the micro-LED assemblies 20.

[0030] FIG. 5 shows a perspective view of the micro-LED display assembly in accordance with aspects of the present disclosure. More specifically, FIG. 5 shows a plurality of micro-LED assemblies 20 mounted on the interposer 30. In embodiments, the plurality of micro-LED assemblies 20, e.g., at least two ILED dies, each contain a plurality of LED pixels 10 with TSV interconnects, placed with equal spacing on the interposer 30. The BEOL interposer 35 is positioned between the plurality of micro-LED assemblies 20 and the interposer 30. The interposer 30 includes solder connections 55 to provide external interconnects for the micro-LED assemblies 20.

[0031] FIG. 6 shows a flowchart of the fabrication processes in accordance with aspects of the disclosure. Particularly, to fabricate the structures shown in FIGS. 2-5, the LED devices, e.g., pixels 10, are fabricated on a wafer using conventional CMOS fabrication processes, at step 600. At step 605, the wafer is flipped over and a backside grinding process is performed. In embodiments, the backside grinding process can thin the wafer, e.g., Si, to about 50 microns. At step 610, a backside of the wafer then undergoes a deep Si etch, e.g., Bosch etch, to form vias, aligned with and exposing the pads formed on the front side of the wafer (and which are in electrical contact with the pixels). At step 615, a dielectric liner is formed in the vias. The dielectric liner can be, e.g., an organic spin on material (SiCOH) or a polyimide material. In embodiments, the dielectric liner would be deposited to a thickness of about 200 nm. At step 620, a barrier metal can be formed over the dielectric liner to prevent Cu diffusion into the oxide and wafer. In embodiments, the barrier metal can be Ta or TiN, deposited by a sputter chemical vapor deposition process. At step 625, an electroplating process is performed. For example, a seed layer is sputtered onto the barrier metal, followed by filling of the via with an electroplating process, e.g., Cu electroplating process. At step 630, any residual material can be removed from the backside surface of the wafer by a chemical mechanical polishing (CMP) process. At step 635, an interconnect can be formed in direct electrical connection to the metal material of the TSV. At step **640**, the micro-LED arrays can be assembled into a larger array by connecting each of the micro-LED arrays to an interposer, as an example.

[0032] The method(s) as described above is used in the fabrication of integrated circuit chips. The resulting integrated circuit chips can be distributed by the fabricator in raw wafer form (that is, as a single wafer that has multiple unpackaged chips), as a bare die, or in a packaged form. In the latter case the chip is mounted in a single chip package (such as a plastic carrier, with leads that are affixed to a motherboard or other higher level carrier) or in a multichip package (such as a ceramic carrier that has either or both surface interconnections or buried interconnections). In any case the chip is then integrated with other chips, discrete circuit elements, and/or other signal processing devices as part of either (a) an intermediate product, such as a motherboard, or (b) an end product. The end product can be any product that includes integrated circuit chips, ranging from toys and other low-end applications to advanced computer products having a display, a keyboard or other input device, and a central processor.

[0033] The descriptions of the various embodiments of the present disclosure have been presented for purposes of illustration, but are not intended to be exhaustive or limited to the embodiments disclosed. Many modifications and variations will be apparent to those of ordinary skill in the art without departing from the scope and spirit of the described embodiments. The terminology used herein was chosen to best explain the principles of the embodiments, the practical application or technical improvement over technologies found in the marketplace, or to enable others of ordinary skill in the art to understand the embodiments disclosed herein.

- 1. A structure, comprising:

- an interposer;

- a plurality of light emitting diode (LED) arrays each of which comprise a plurality pixels composed of multiple sub-pixels; and

- a plurality of through-vias each of which are separately connecting each of the plurality of pixels of each separate of the plurality of LED arrays to the interposer.

- 2. The structure of claim 1, wherein the interposer is a silicon interposer with driver circuits.

- 3. The structure of claim 1, wherein the interposer is a glass interposer.

- **4**. The structure of claim **1**, wherein the through-vias are through silicon vias.

- **5**. The structure of claim **4**, wherein each of the pixels is connected to the interposer by a separate silicon via technology.

- **6.** The structure of claim **1**, wherein the pixels are composed of GaN and the through-vias are copper through silicon vias integrated into a same die as the pixels.

- 7. The structure of claim 1, wherein the through-vias are connected to the interposer by pillars which match a pitch of the through-vias.

- **8**. The structure of claim **1**, wherein the plurality of LED arrays are equally spaced apart on the interposer.

- **9**. The structure of claim **8**, wherein an across die pixel pitch is equal to a pixel pitch/spacing within each of the plurality of LED arrays.

- 10. The structure of claim 1, wherein a diameter of the through vias is about ½ a pixel pitch.

- 11. A structure comprising:

- an interposer comprising a plurality of through vias;

- a plurality of light emitting diode (LED) arrays each of which comprise a plurality of through-vias connecting to each pixel of the plurality of LED arrays, wherein each pixel is composed of multiple sub-pixels; and

- a back-end of the line wiring scheme which connects the plurality of through-vias of each of the pixels to the plurality of through vias of the interposer by separate pillars aligned with each of the plurality of through-vias of each of the pixels.

- 12. The structure of claim 11, wherein:

- the plurality of LED arrays are equally spaced apart; and an across die pixel pitch is equal to a pixel pitch within each of the plurality of LED arrays.

- 13. The structure of claim 12, wherein the pixels are composed of GaN and the through-vias of the plurality of the plurality of LED arrays are copper through silicon vias integrated into a same die as the pixels.

- 14. The structure of claim 13, wherein the through silicon vias are connected to the back end of the line wiring scheme by the pillars.

- 15. The structure of claim 14, wherein the pillars are solder connections.

- **16**. The structure of claim **14**, wherein the pillars match a pitch of the through silicon vias.

- 17. The structure of claim 13, wherein a diameter of each through-via is about  $\frac{1}{2}$  a pixel pitch.

- **18**. The structure of claim **11**, wherein the back-end of the line interposer is a silicon interposer with driver circuits.

- 19. The structure of claim 11, wherein the back-end of the line interposer is a glass interposer.

- 20. (canceled)

- 21. The structure of claim 1, further comprising a backend of the line wiring scheme which is interposed between the interposer and the plurality of LED arrays, the backend of the line wiring scheme connects the each of the plurality of through-vias of each of the pixels to the interposer by separate pillars aligned with each of the plurality of through-vias of each of the pixels.

\* \* \* \* \*

| 专利名称(译)        | 微型LED显示器组件                                                                                                |         |            |  |

|----------------|-----------------------------------------------------------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | <u>US20180269191A1</u>                                                                                    | 公开(公告)日 | 2018-09-20 |  |

| 申请号            | US15/459336                                                                                               | 申请日     | 2017-03-15 |  |

| [标]申请(专利权)人(译) | 格罗方德半导体公司                                                                                                 |         |            |  |

| 申请(专利权)人(译)    | GLOBALFOUNDRIES INC.                                                                                      |         |            |  |

| 当前申请(专利权)人(译)  | GLOBALFOUNDRIES INC.                                                                                      |         |            |  |

| [标]发明人         | ENGLAND LUKE<br>PAWLAK BARTLOMIEJ JAN                                                                     |         |            |  |

| 发明人            | ENGLAND, LUKE<br>PAWLAK, BARTLOMIEJ JAN                                                                   |         |            |  |

| IPC分类号         | H01L25/16 H01L25/075 H01L25/00 H01L33/62 H01L33/32                                                        |         |            |  |

| CPC分类号         | H01L25/167 H01L25/0753 H01L27/1214 H01L33/62 H01L33/32 H01L25/50 H01L27/15 H01L27/156 H01L33/18 H01L33/24 |         |            |  |

| 外部链接           | Espacenet USPTO                                                                                           |         |            |  |

|                |                                                                                                           |         |            |  |

# 摘要(译)

本发明涉及半导体结构,更具体地,涉及微发光二极管(LED)显示组件和制造方法。该结构包括插入器和多个微LED阵列,每个微LED阵列包括将多个微LED阵列的像素连接到插入器的多个通孔。